Recently, the paper “DDP-Fsim: Efficient and Scalable Fault Simulation for Deterministic Patterns with Two-Dimensional Parallelism” from the State Key Lab of Processors was nominated as a Best Paper Award Candidate at ICCAD 2024, a CCF-recommended Category B international conference. The first author of the paper is Master’s student Gu Feng (supervised by Associate Researcher Ye Jing).

As semiconductor process nodes continue to shrink and the complexity of integrated circuit design increases, Design for Test (DFT) has become an essential aspect of very large-scale digital circuit design. It computes the fault coverage of Automatic Test Pattern Generation (ATPG). During the DFT process, fault simulation is used to assess and verify whether potential manufacturing defects can be effectively detected. Its performance directly impacts the efficiency of ATPG algorithms. In recent years, the widespread adoption of multi-core processor architectures has driven the development of parallel fault simulation techniques, greatly improving simulation efficiency by distributing tasks across multiple cores. However, most existing methods focus on optimizing simulation speed for random patterns and overlook optimization for deterministic patterns generated by ATPG. The proposed DDP-Fsim algorithm addresses this gap by splitting the simulation flow into two phases—fault-dimension parallelism and pattern-dimension parallelism—based on the characteristics of deterministic patterns. It introduces fanout-free region (FFR) as the ideal scheduling unit to improve load balancing and reduce scheduling overhead. Experimental results show that on a 24-core system, DDP-Fsim achieves a 16× speedup compared to a single-core system, whereas leading commercial tools only reach 3–6×. DDP-Fsim also maintains a stable speedup when handling large-scale circuits, demonstrating its strong scalability. The methods proposed in this work were applied to the EDA contest EDA2 Xiake Island Problem Challenge “Parallel Acceleration of Fault Simulation Based on ARM Multi-core CPU Architecture” (provided by HiSilicon corporation). In March 2024, the team comprising graduate students Feng Gu, Mingjun Wang, and Jiaping Tang (co-authors of the paper) from the State Key Lab of Processors outperformed several dozen other teams to secure first place in this contest.

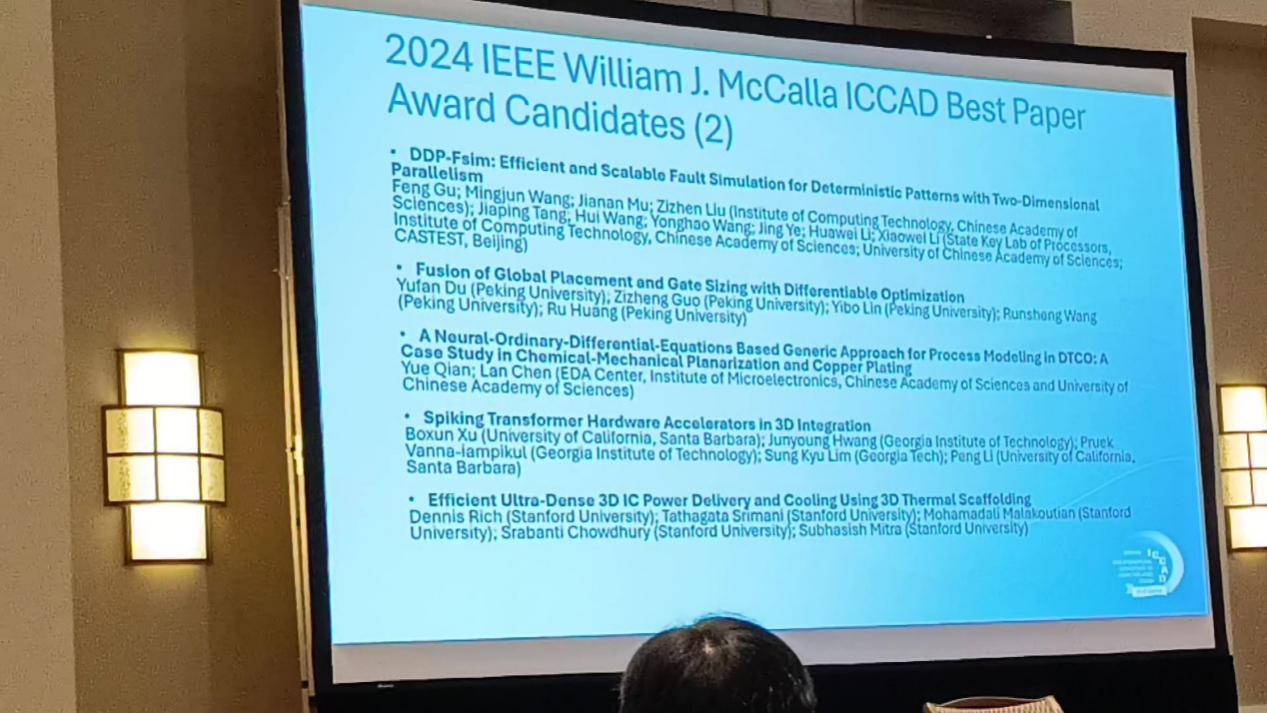

Jointly sponsored by the Institute of Electrical and Electronics Engineers (IEEE) and the Association for Computing Machinery (ACM), the International Conference on Computer-Aided Design (ICCAD) is highly regarded and influential in the EDA field. The 43rd ICCAD took place in Newark, New Jersey, from October 27 to October 31, 2024, with 195 papers accepted in total. Of these, 10 were nominated for the Best Paper Award, and ultimately 2 papers received the award.

downloadFile