The paper “Towards Developing High Performance RISC-V Processors Using Agile Methodology” from the XiangShan Team of the Center for Advanced Computer Systems (ACS), Institute of Computing Technology (ICT), Chinese Academy of Sciences (CAS), was published at the 55th IEEE/ACM International Symposium on Microarchitecture (MICRO 2022, CCF-A). The ACS-written paper was subsequently selected as an IEEE Micro Top Pick, chosen from among 130 competitive papers at the four 2022 computer architecture conferences, based on the criteria of researches having “the most novelty and potential for long-term impact.”

This is the second time that ICT has won this prestigious award. In 2014, ICT’s "DianNao" intelligent processor team had won a Top Pick award. Out of all submissions from China’s computing institutes, only two have been awarded a Micro Top Pick, and both came from ICT. This demonstrates the lead ICT/CAS has within the field of computer architecture research.

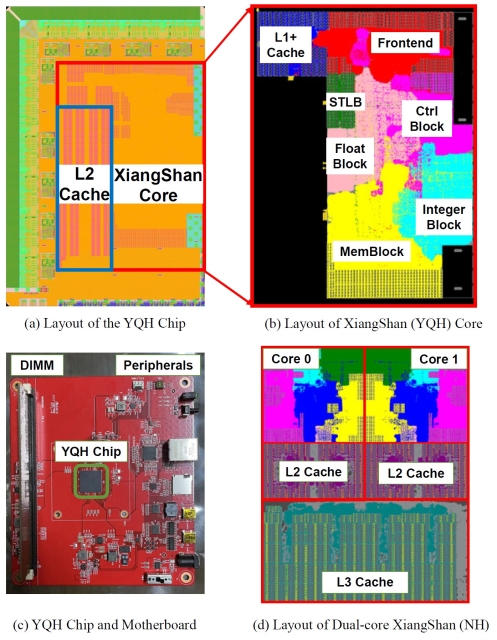

Figure. XiangShan layout, chips, and motherboard

Open-source hardware and hardware agile development methods have captured the attention of academia and industry experts in recent years, but these innovations have few industrial applications, as yet. There are two reasons why: agile development methods have not been applied to industrial-grade high-performance open-source processor projects, and completion of agile verification of complex processor projects remains problematic.

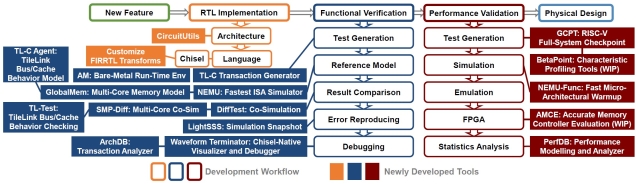

XiangShan is an open-source high-performance processor developed by ICT-CAS, and ICT’s Xiangshan Team continues to research agile development methods for open-source chips and processors. To address the issues of function verification and debugging for processors, the XiangShan team introduced the chip agile development platform "MinJie." To improve hardware verification efficiency, the team’s award-winning paper proposed novel DiffRules to describe the non-deterministic design behavior, effectively reducing development and maintenance costs of reference models and verification frameworks. The paper presents some sources of non-deterministic behavior in RISC-V processors and implements a co-simulation framework DiffTest for verifying RISC-V processors. This has been successfully applied to XiangShan, One Student One Chip (OSOC), and other projects. The paper also proposes a lightweight simulation snapshot technology LightSSS that uses the fork provided by the operating system to reduce the overhead of simulation snapshots. Evaluation results showed LightSSS has significant advantages over the state-of-the-art simulation snapshot solution with orders of magnitude less overhead.

Figure. The MinJie agile development infrastructures

The XiangShan project has obtained more than 3,500 stars on GitHub with more than 440 forks, placing it among the most popular open-source hardware projects worldwide. It is recognized by RISC-V International as the highest-performance open-source RISC-V processor. In addition, to establish a continuously advancing, competitive and open hardware ecosystem, the non-profit organization Beijing Institute of Open Source Chip (BOSC) was established with industry-leading companies as founding members. Recently, the XiangShan team hosted a tutorial at the ASPLOS 2023 conference (CCF-A) to introduce to the research community the XiangShan and MinJie infrastructures, which are expected to be an innovative research platform for the computer architecture community from academia and industry.

The 2022 MICRO Conference, which resulted in attention for XiangShan and MinJie, was held in Chicago, Illinois, USA from October 1-5, 2022. The conference received 369 submissions and accepted 83 papers, an acceptance rate of only 22.5%. This IEEE/ACM International Symposium on Microarchitecture (MICRO for short) is the premier forum for presenting, discussing and debating innovative microarchitecture ideas and techniques for advanced computing and communication systems. The symposium, the 55th one to be held, brought together global researchers in microarchitecture, compilers, chips and systems for technical exchange on traditional microarchitecture topics and emerging research.

IEEE Micro has been publishing its annual “Top Picks from the Computer Architecture Conferences” issue since 2003, and it is a distinguished honor for ICT’s XiangShan and MinJie to be recognized. The Top Picks special issue collects some of the most significant research papers in computer architecture based on novelty and long-term potential. The IEEE Micro Top Picks award is selected from about 300 papers published at that year’s four top conferences on computer architecture (ASPLOS/HPCA/ISCA/MICRO). The Top Picks Selection Committee chooses the most significant, insightful papers that show potential to influence the work of computer architects for years to come. A total of 130 papers were submitted this year, setting a record for applications. Among them, only 12 papers were awarded Top Picks, and another 12 papers were awarded nomination awards.

downloadFile