A joint research team from the Institute of Computing Technology, CAS, and from Shenzhen Institute for Quantum Science and Engineering, SUSTech, has implemented a novel quantum version of AND logic gate. This new development within the field of quantum algorithm implementation and quantum architecture reduces resource overhead when implementing AND logic on quantum hardware, thus enabling execution of key quantum circuits. The findings were published under the title "Scalable algorithm simplification using quantum AND logic" in Nature Physics on November 14, 2022.

With quantum computing predicted to provide computational speed-up for several practical problems (i.e., database search and integer factorization), the quantum circuit which describes the quantum algorithm needs to be decomposed into the naturally available elementary gates so as to implement that algorithm on the specified device. Given near-term quantum devices’ resource constraints, optimizing the quantum circuits for describing quantum algorithms can be critical for realizing near-term applications. This optimization is as important as enhancement of qubit quality.

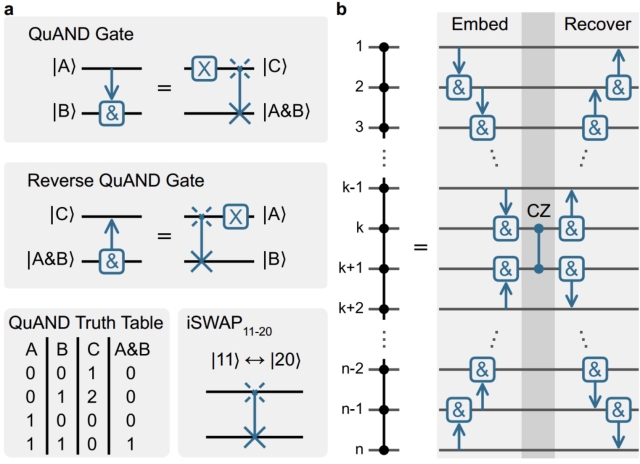

a. Decomposition, truth table of QuAND and its reversal b. Decomposition of multi-qubit-controlled Z gate

This work involved the research team’s proposal for a quantum version of AND gate (QuAND). AND logic is a basic ingredient for design algorithms in traditional computer science. QuAND gate, by enriching the quantum instruction set toolbox, can significantly reduce the cost of decomposing some important large-scale quantum circuits, such as multi-qubit Toffoli gates and quantum arithmetic circuits. The joint team developed a superconducting quantum processor, consisting of 8 qubits, that utilizes the latest tunable coupler combined with fixed frequency bits. Advantages were seen in high scalability and simplified control. During the experiment, the high-fidelity QuAND gate was implemented by applying a parametric flux drive to the coupler.

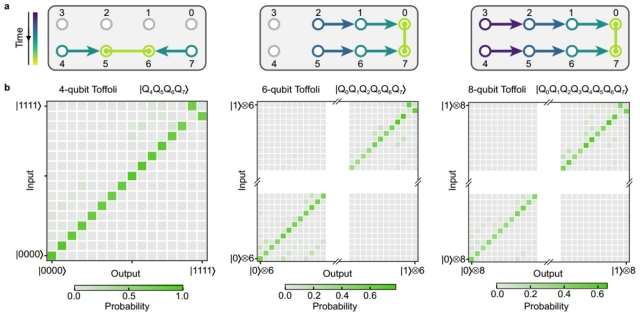

The QuAND-based decomposition and measured truth table of 4-qubit, 6-qubit and 8-qubit Toffoli.

The research team successfully implemented a multi-qubit Toffoli gate of up to 8 qubits. This QuAND gate-based optimization method requires only a linear number of two-bit gates, whereas traditional methods would require a quadratic number two-bit gate. The experimental team succeeded at implementing the largest multi-qubit Toffoli gate to date because of the dramatic reduction in gate operation overhead. On a much larger experimental scale than before, the research team also demonstrated the Grover search algorithm up to a 64-entries search space. This work demonstrates how non-traditional but hardware-native quantum logic gate operations can be constructed on scalable quantum computin g hardware to optimize the compiled results of quantum algorithms to quantum circuits. The work illustrates the importance of tapping the manipulation potential of quantum hardware and enriching the set of quantum instruction sets, laying the foundation for more meaningful future applications of larger scale.

Ref link: https://doi.org/10.1038/s41567-022-01813-7

downloadFile