The Key Laboratory of Processors is aimed at the frontier innovation theory of processors in this Post-Moore era, including both theoretical research and prototype tool development.

Three areas are the current priorities

Microarchitecture

Processor architecture and domain-specific accelerators for novel applications are the focus in this area, with specific emphasis on the architecture theory of universality and energy efficiency, and the design space search of software-hardware codesign.

Processor Design Automation

Processor front-end toolchain supporting domain-specific optimization including function simulation, circuit synthesis, and verification and design for test are the primary development goals.

Programming Technology

Unified software stack for cross platforms, compiler optimization and middleware of software stack are under development in the Key Laboratory of Processors.

Previous Achievements

Our research has made several breakthrough achievements in the field of processors in China, including China's first high-performance general-purpose processor chip, Loongson No.1, and the first international deep learning processor chip, Cambrian No.1, etc.

Our institute was also one of the earliest research institutions in China that initiated the EDA and compiling research during 1970s and later.

Three areas are the current priorities

Microarchitecture

Processor architecture and domain-specific accelerators for novel applications are the focus in this area, with specific emphasis on the architecture theory of universality and energy efficiency, and the design space search of software-hardware codesign.

Processor Design Automation

Processor front-end toolchain supporting domain-specific optimization including function simulation, circuit synthesis, and verification and design for test are the primary development goals.

Programming Technology

Unified software stack for cross platforms, compiler optimization and middleware of software stack are under development in the Key Laboratory of Processors.

Previous Achievements

Our research has made several breakthrough achievements in the field of processors in China, including China's first high-performance general-purpose processor chip, Loongson No.1, and the first international deep learning processor chip, Cambrian No.1, etc.

Our institute was also one of the earliest research institutions in China that initiated the EDA and compiling research during 1970s and later.

Some of the previous achievements are listed below:

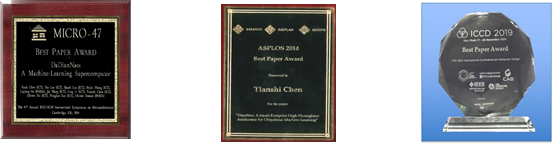

DianNao: a small-footprint high-throughput accelerator for ubiquitous machine-learning

Best Paper Award at 19th ASPLOS in 2014, which has been the only BPA obtained by research groups from Asia since the initiation of ASPLOS.

DaDianNao: A Machine-Learning Supercomputer

Best Paper Award at 47th MICRO in 2014, which has been the only BPA obtained by research groups from Asia since the initiation of MICRO.

PuDianNao: A Polyvalent Machine Learning Accelerator

Published at 20th ASPLOS in 2015, which presented the first general machine learning processor architecture in the world.

EnGN: A High-Throughput and Energy-Efficient Accelerator for Large Graph Neural Networks

Best Paper Award from IEEE Transactions on Computers in 2021, which presented one of the earliest GNN accelerators.

Level by level: making flow- and context-sensitive pointer analysis scalable for millions of lines of code

Published at CGO 2010, and obtained the Test-of-Time Award in CGO 2021, which has been the only Test-of-Time Award obtained by research groups from Asia since the initiation of CGO.

RRAMedy: Protecting ReRAM-based Neural Network from Permanent and Soft Faults During Its Lifetime

Best Paper Award at 37th ICCD in 2019, which has been the 1st conference-only BPA obtained by research groups from Mainland China since the initiation of ICCD.

Godson-3: A Scalable Multicore RISC Processor with x86 Emulation

Presented the microarchitecture design of Godson-3, the first multi-core processor in China, which proposed a scalable multi-core architecture based on cross-switching and mesh networks, and a reconfigurable design that supports x86 instruction translation. Published at MICRO 2009, it is also the 1st paper from Mainland China since the initiation of MICRO.

DaDianNao: A Machine-Learning Supercomputer

Best Paper Award at 47th MICRO in 2014, which has been the only BPA obtained by research groups from Asia since the initiation of MICRO.

PuDianNao: A Polyvalent Machine Learning Accelerator

Published at 20th ASPLOS in 2015, which presented the first general machine learning processor architecture in the world.

EnGN: A High-Throughput and Energy-Efficient Accelerator for Large Graph Neural Networks

Best Paper Award from IEEE Transactions on Computers in 2021, which presented one of the earliest GNN accelerators.

Level by level: making flow- and context-sensitive pointer analysis scalable for millions of lines of code

Published at CGO 2010, and obtained the Test-of-Time Award in CGO 2021, which has been the only Test-of-Time Award obtained by research groups from Asia since the initiation of CGO.

RRAMedy: Protecting ReRAM-based Neural Network from Permanent and Soft Faults During Its Lifetime

Best Paper Award at 37th ICCD in 2019, which has been the 1st conference-only BPA obtained by research groups from Mainland China since the initiation of ICCD.

Godson-3: A Scalable Multicore RISC Processor with x86 Emulation

Presented the microarchitecture design of Godson-3, the first multi-core processor in China, which proposed a scalable multi-core architecture based on cross-switching and mesh networks, and a reconfigurable design that supports x86 instruction translation. Published at MICRO 2009, it is also the 1st paper from Mainland China since the initiation of MICRO.

Best Paper Awards

downloadFile