Zijian Jiang, the first-year master's student at the Center for Advanced Computer Systems, the Institute of Computing Technology, Chinese Academy of Sciences, has his paper "Corvus: Efficient HW/SW Co-Verification Framework for RISC-V Instruction Extensions with FPGA Acceleration" accepted by ASP-DAC 2025, the largest conference in Asia and South-Pacific regions on Electronic Design Automation (EDA). His advisor is Dr. Kan Shi.

ASP-DAC (Asia and South Pacific Design Automation Conference) is recognized alongside DAC, ICCAD, and DATE as one of the four major conferences in the field of EDA. It encompasses the most advanced achievements in electronic design automation each year, attracting the attention and participation of scholars from around the world. Since its inception 30 years ago, ASP-DAC has become a premier platform for renowned scholars and industry experts in the global EDA field to exchange ideas. This year’s conference will take place in Tokyo, Japan, with 587 submissions received and 168 papers accepted, yielding an acceptance rate of 28.62%.

Introduction

Corvus: Efficient HW/SW Co-Verification Framework for RISC-V Instruction Extensions with FPGA Acceleration

Author: Zijian Jiang (ICT/CAS), Keran Zheng (Imperial College London), David Boland (The University of Sydney), Yungang Bao (ICT/CAS), Kan Shi (ICT/CAS)

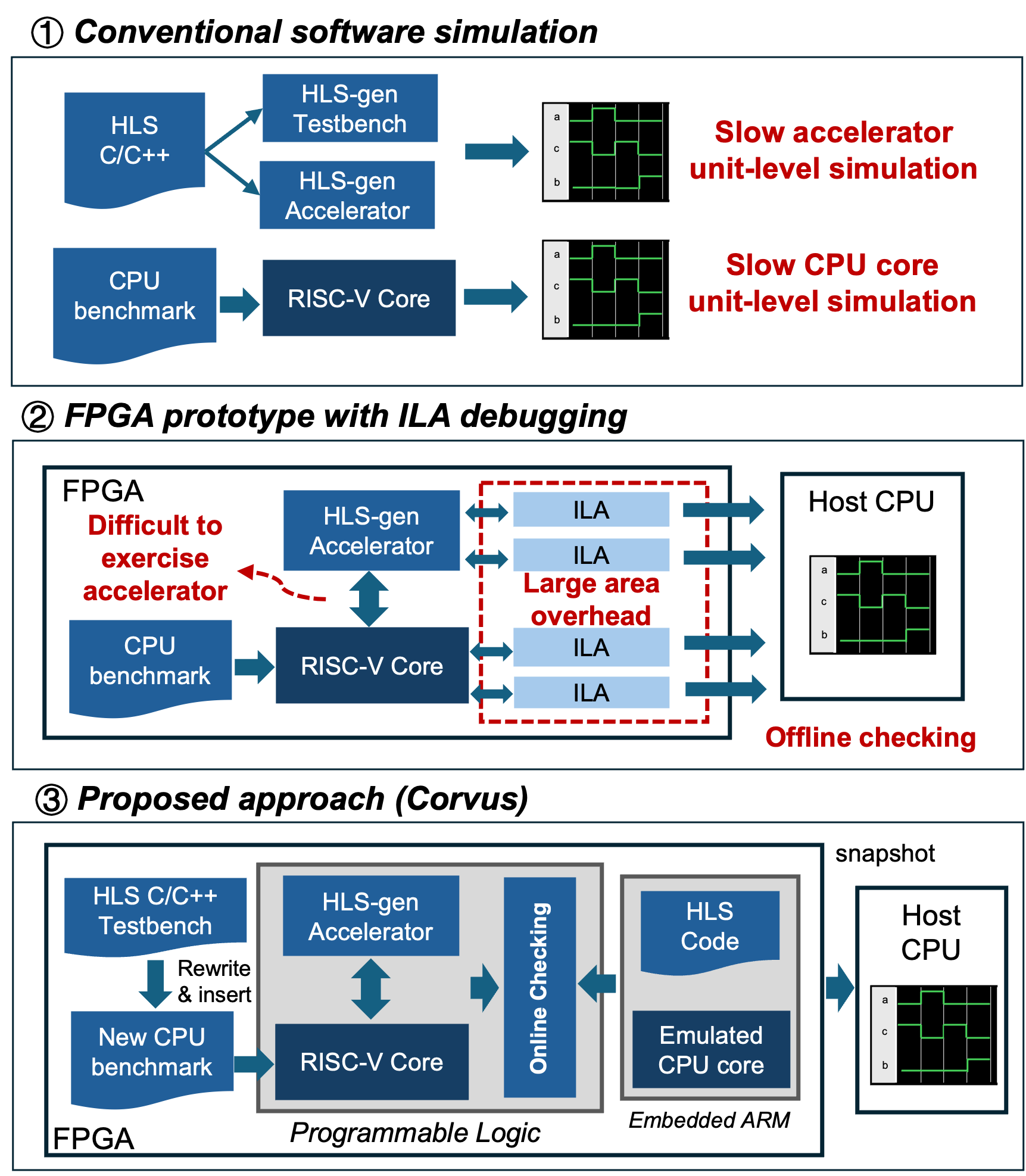

The RISC-V instruction set architecture (ISA) offers flexibility for domain-specific custom instruction extensions. While the basic RISC-V ISA contains common instructions, the extended accelerators provide additional computing power to meet diverse needs. High-level synthesis (HLS) is often used to agilely create custom extension accelerators, allowing engineers to design complex digital circuits using high-level languages such as C/C++, further improving development efficiency. However, verifying a design that includes RISC-V cores and custom extensions is rarely studied and can be challenging. Traditional approaches for verifying HLS-generated designs use C-RTL co-simulation, primarily focusing on the unit level. This method can be extremely time-consuming and often makes impractical assumptions about interactions between HLS-generated circuits and the processor. Therefore, system-level verification is essential to extensively exercise the RISC-V cores, the custom extensions, and their interconnections.

Figure 1: Conventional verification approaches for RISC-V custom extensions vs. the proposed method using Corvus.

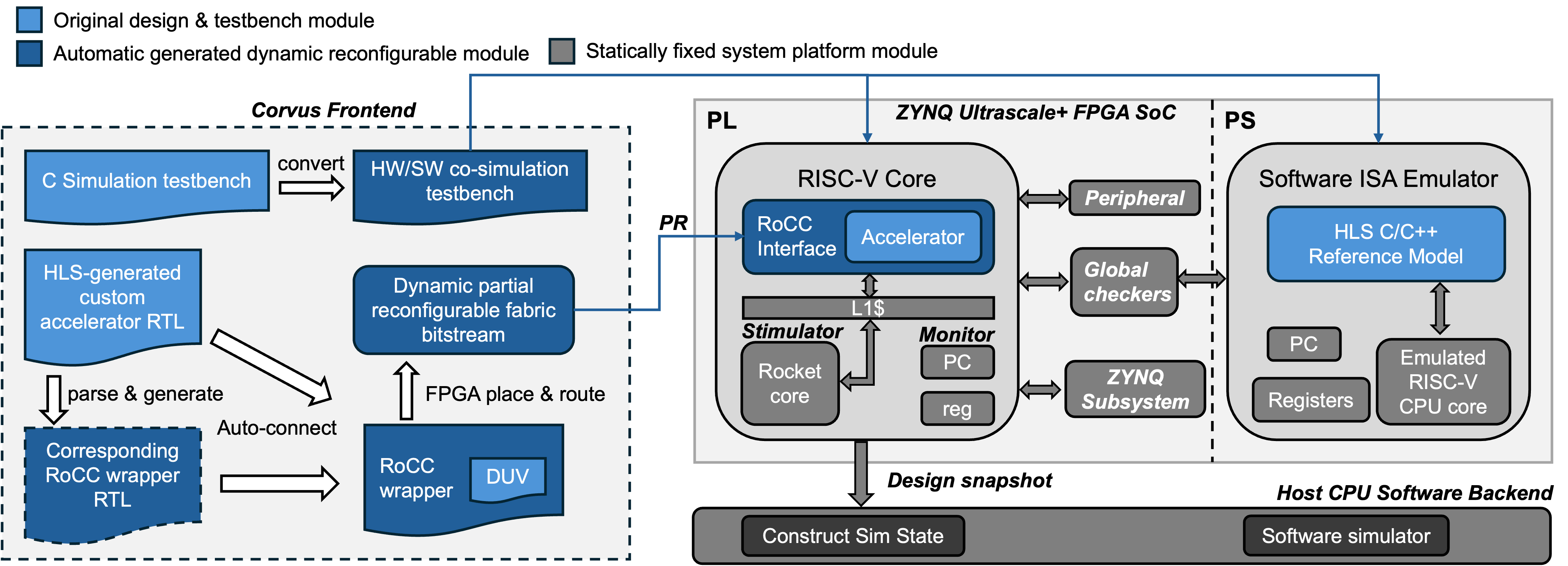

To efficiently verify a RISC-V processor design with custom instruction extensions, we propose Corvus: a novel co-verification framework that combines the benefits of the high-level abstraction of C/C++ simulation and cycle-accurate modeling of C-RTL co-simulations. Corvus provides hardware wrapper templates that efficiently connect HLS-generated accelerators and the RISC-V core, and a tool flow that automatically translates HLS unit-level tests into system-level stimulus. Corvus maps the core and the accelerators, along with their corresponding C/C++ software models, onto the same FPGA with hardened processors, allowing them to run simultaneously whilst checking both results on the fly with dedicated hardware monitors and checkers. If a mismatch is detected, we capture a snapshot of the accelerator hardware and reconstruct the simulation in external software simulators for detailed debugging. When potential issues are fixed, the accelerator region can be partially reconfigured without recompiling the entire design, further improving the design-verification efficiency. Results show a significant performance improvement over conventional approaches, from 4423× to 16626×.

Figure 2: Corvus workflow

Information

Zijian Jiang, Keran Zheng, David Boland, Yungang Bao, and Kan Shi. Corvus: Efficient HW/SW Co-Verification Framework for RISC-V Instruction Extensions with FPGA Acceleration. In 30th Asia and South Pacific Design Automation Conference (ASP-DAC’25). January 2025.

Dr. Kan Shi's research group focuses on the development of key technologies for agile verification and hardware acceleration. Their major research projects include the FPGA-based agile verification platform ENCORE, which has been extended and applied in various areas such as hardware assertions and high-level synthesis verification. These outcomes have been used for the agile verification of several open-source RISC-V processor cores and high-level synthesis designs. The results have been published in several international academic conferences and journals, including FPGA, ASPLOS, and ASP-DAC. The group is continuously recruiting full-time engineers, postdoctoral researchers, and interns. Please contact: shikan@ict.ac.cn.

downloadFile